介绍如何构建最小系统。

简介

本章中将介绍如何构建单片机最小核心系统,包括电源设计、下载接口选择、晶振选择等等。

文章比较长,可以点开左侧目录快速查阅。

电源电路设计

供电电压范围

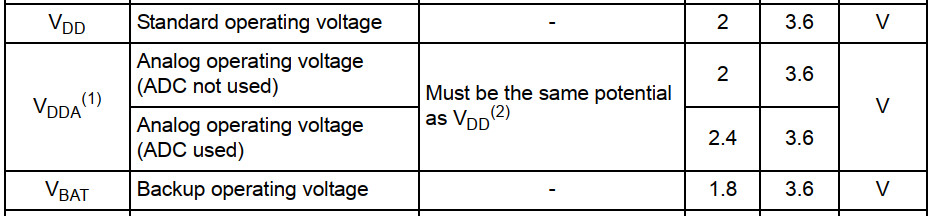

以 STM32F103RCT6 为例。一般,芯片手册中都会给出芯片的引脚定义、封装信息以及推荐电路。注意,STM32F103RCT6 的数据手册是 STM32F103 系列共用的。微控制器的供电大致分为两种,分别是 3V3 供电和 5V 供电,在数据手册中会给出,如下所示。下图说明,STM32F103 系列 VDD 引脚供电范围在 2~3.6V 之间;如果不使用 ADC 功能,那么 VDDA 的供电电压可以是 2~3.6V 之间,如果使用了 ADC 功能,那么 VDDA 的供电电压必须在 2.4~3.6V 之间;备份域供电电压可在 1.8~3.6V 之间。所以我们可以将芯片的供电电压定为 3.3V。

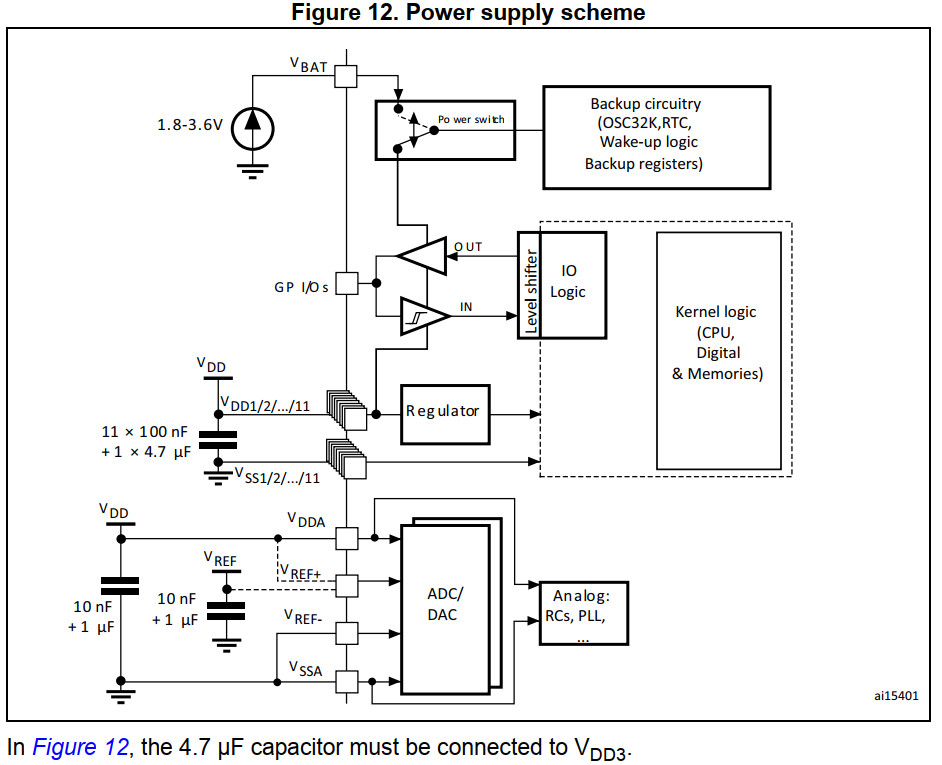

官方的参考电路

在数据手册电器特性一章,有给出推荐的电源电路设计,如下所示。官方推荐的电路中,电源电路设计主要分为三大块,一是备份域(RTC 和备份寄存器)供电,二是数字域供电,三是模拟域供电。

备份域供电

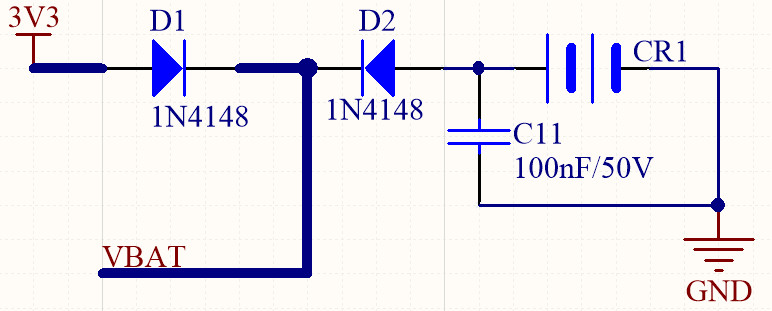

备份域中包含了 RTC 实时时钟模块,如果项目中有用到 RTC,为了 RTC 正常运行,需要给芯片外接一个纽扣电池,用于断电后维持 RTC 的运行。一般,纽扣电池电路的设计可以如下所示。

右上角的 CR1 即为纽扣电池座子,用来安装纽扣电池,如下所示。当然也可以是其它类型的座子。

这里用了两个二极管来选择 VBAT 到底是使用哪一路输出。一般纽扣电池的电压在 1.5~3V 之间。电路板未断电时,D1 左侧有电源输入,因为 3V3 电源电压比纽扣电池高,所以 D1 导通,D2 阻断,VBAT 由 3V3 电源提供;电路板断电后,D1 左侧没有电源输入,D2 导通,VBAT 由纽扣电池提供。

通过参考电路的内部结构,我们可以看到,其实 STM32F103RCT6 芯片内部已经对 VDD 和 VBAT 做了二选一的操作,显得我们的纽扣电池电路很多余。但是,有些芯片内部是没有做这个处理的,所以为了适配所有的应用场景(主要是懒),可以在外边额外再包一层二选一的电路。

如果项目中没有应用到 RTC 实时时钟,那么可以简单的将 VBAT 直接连到 VDD。

数字域供电

STM32F103RCT6 的 IO 逻辑电路、CPU、内存以及其它数字域,是由 VDD 引脚提供电源的。数字域中含有 CPU,即 Cortex-M 内核,是耗电量最大的区域,所以一般会有多个 VDD 引脚,这些引脚都要连到 3V3 供电。除此之外,每个 VDD 引脚附近都至少要有一个 100nF 的去耦电容,用于提高电路抗干扰能力;PCB 布局时,去耦电容要尽可能靠近芯片摆放,如果是双面布局,那么可以考虑将去耦电容放置到芯片的背面。

模拟域供电

STM32F103RCT6 的 ADC、DAC、PLL 等,是由 VDDA 引脚供电。相对而言,VDDA 引脚的数量要比 VDD 少得多,那是因为数字域的功耗不高。对于高端一些的芯片,ADC 和 DAC 拥有独立的参考电压引脚。用户可以用一个高精度、低温漂的稳压管为模拟域提供可靠的参考电压,这样测出来的 ADC 值会更精确。对于 VDDA 引脚,因为模拟域对噪声很敏感,需要做更多的滤波,所以去耦电容通常是一大一小搭配。对于数字域和模拟域的供电,一般用 10uH 的电感隔开,可以起到简单的数模隔离效果。

小节

一般,芯片的电源供电可以直接使用数据手册里提供的参考电路。这个电路是经过官网验证过的,肯定没问题。当然,如果手上已经有成熟的电路,那么可以直接照搬。芯片的去耦电容只是起到滤波的作用,就算是没有,芯片也是能正常运行的,就是抗干扰性没那么强,一般情况下也能正常使用。

复位电路设计

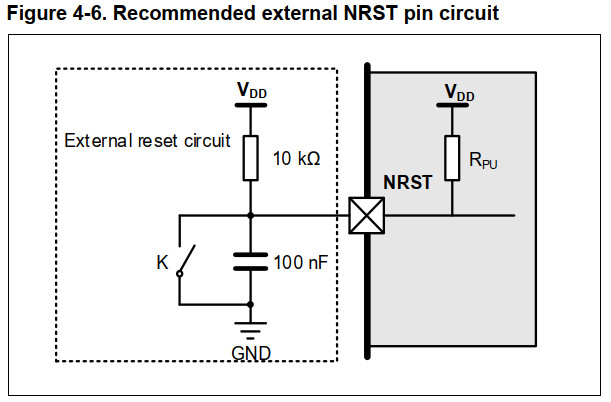

同样的,在 STM32F103RCT6 的数据手册中,官方也给出了复位相关的推荐电路,如下所示。可以看到,在 STM32F103RCT6 芯片内部,复位引脚 NRST 是有默认上拉的。所以即使用户将 NRST 引脚悬空,芯片也是能正常运行。实际项目中推荐保留复位电路,复位按键在调试中特别有用,常常会需要手动复位芯片,如果电路板上没有复位按键,那将会很尴尬。

启动模式选择电路设计

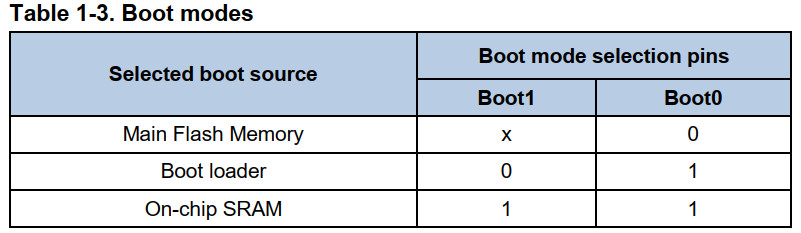

在 STM32F103RCT6 芯片中,由有两个特殊引脚,BOOT0 和 BOOT1,用来控制芯片的启动方式,在参考手册(非数据手册)中有详细介绍,如下所示。复位后,芯片会在启动瞬间检测 BOOT0 和 BOOT1 引脚的电平,根据引脚电平选择不同的启动方式。

其中,Main Flash Memory 即为运行用户烧录到 Flash 中的程序,一般芯片是工作在这个模式。Boot loader 模式即为 ISP 烧录,即串口烧录模式。在该模式下,用户可以将程序文件烧录到 Flash 中,我们用一键下载烧录程序时,芯片就是工作在这个模式。On-chip SRAM 是指运行 SRAM 中的程序,一般不用。

对于 BOOT1 引脚,我们大可直接用 10kΩ 电阻下拉,因为不管是 Main Flash Memory 或 Boot loader 模式,BOOT1 都可以是低电平。

对于 BOOT0 引脚,如果使用 STLink 或 Jlink 等下载器,那么也可以直接用 10kΩ 拉低,下载器会通过协议控制芯片进入烧录模式,无需将 BOOT0 引脚设为 1。如果是使用了一键下载的模式,即 ISP 烧录,那么则需要部署方便 BOOT0 上拉的设计。一键下载电路是可以控制 BOOT0 电平高低的,如果电路中没有一键下载的设计,那么需要用跳线帽或镊子等强制将 BOOT0 拉高,进入 Boot loader 模式,然后再烧写。

下载电路设计

对于下载,可以选择一键下载电路,既可以通信,也可以烧录,一举两得,就是电路复杂了些。另外,还可以使用 STLink 或 JLink 下载器烧录,此时可以选择 JTAG 或 SWD 接口。在这里推荐使用 SWD 接口,标准的 JTAG 接口太大了,SWD 接口只用四根根线,SWDIO、SWCLK、GND 和 VCC,小巧轻便。

单片机的下载分有 ICP、ISP 和 IAP 下载。

ICP(In Circuit Programing),意思为在电路编程。使用 ICP 编程时,需要使用到 STLink 或 JLink 等下载器,通过 JTAG/SWD 下载程序。

ISP(In System Programing),意思为在系统上编程。目标芯片使用 USB/UART/SPI/IIC/RS-485/CAN 等周边接口的 LDROM 引导代码去更新芯片内部 APPROM、数据闪存(DataFlash)和用户配置字节。

IAP(In applicating Programing),是指通过软件实现在线擦除和编程。IAP技术是从结构上将Flash存储器映射为两个存储体,当运行一个存储体上的用户程序时,可对另一个存储体重新编程,之后将程序从一个存储体转向另一个。

一键下载

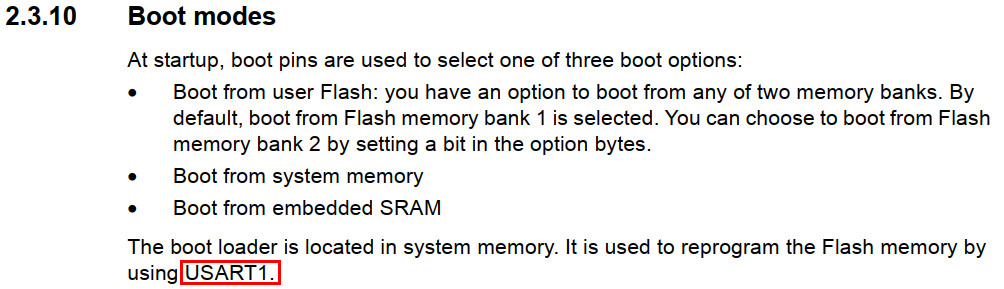

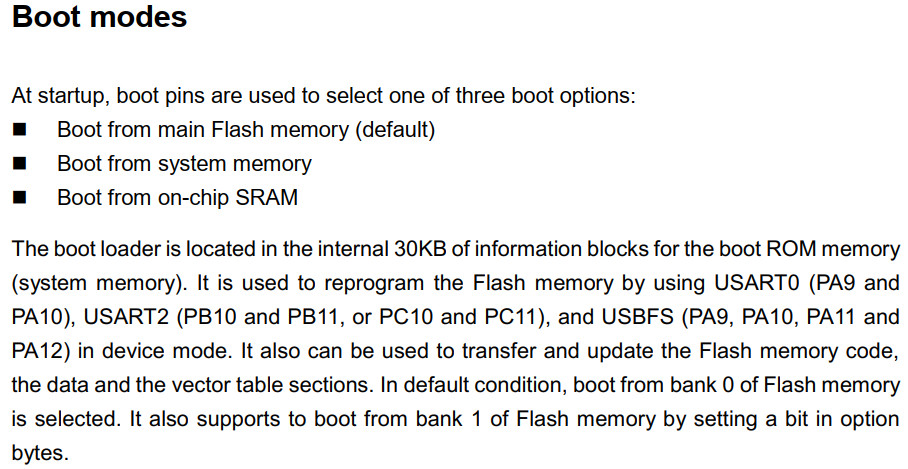

一键下载电路使用的是 ISP 编程。在 STM32F103RCT6 的数据手册中,明确指出了 ISP 对应的接口为 USART1,如下所示。

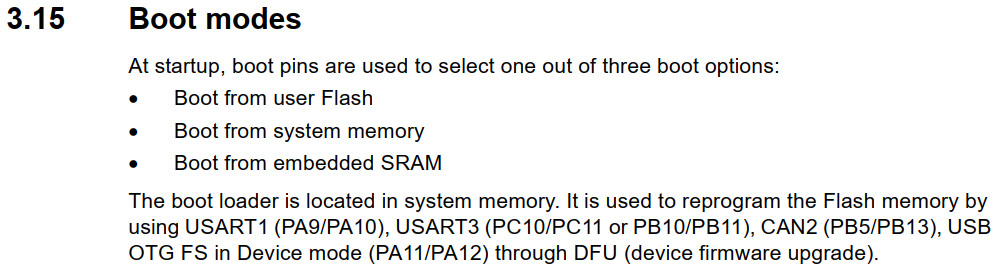

对于 STM32F429IGT6,ISP 下载接口就多了,如下所示。用户不仅可以通过 USART1 下载程序,还能通过 USART3、CAN2、USB 更新固件。

类似的,GD32F470IIH6 也提供了多个接口,用户在制作电路板时,有了更多的选择,如下所示。

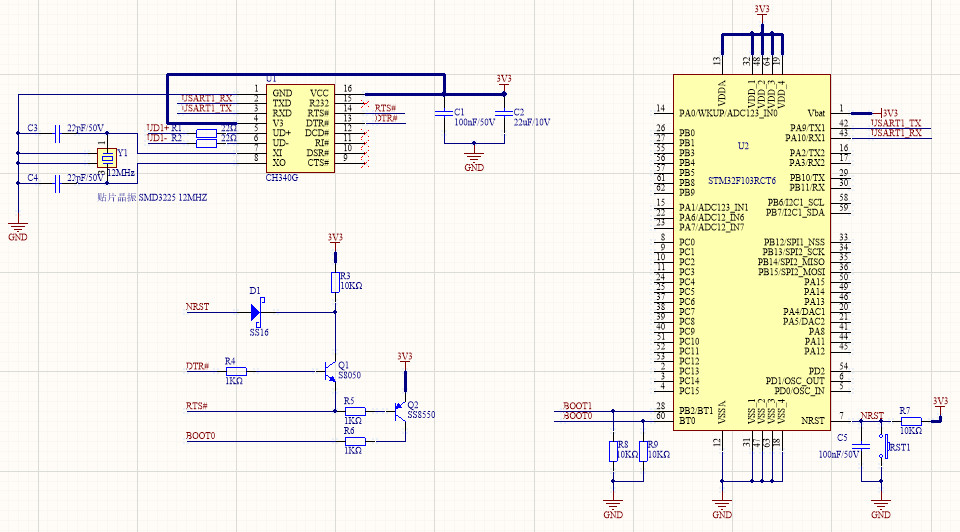

那么多种 ISP 接口中,用的比较多的是 UART接口,与 UART 搭配的一键下载电路如下所示。CH340G 负责 USB 协议和 UART 协议之间的转换,通过 CH340G,可以实现电脑与单片机相互通信。UD1+ 和 UD1- 分别连接到 USB 的 D+ 和 D-,用于连接电脑 USB 接口。USART1_RX 和 USART1_TX 连接到单片机的 ISP 下载引脚,对于 STM32 和 GD32,通常是 PA9(TX) 和 PA10(RX)。

通过前一小节,我们可以得知。要控制芯片进入 ISP 烧录,即 Boot loader 模式,就需要在系统复位启动期间,将 BOOT0 引脚拉高,BOOT1 引脚拉低。一般情况下,BOOT0 和 BOOT1 引脚会外接一个 10KΩ 的下拉电阻,BOOT1 引脚默认输入为低电平,因此只需要控制 BOOT0 引脚的电平即可。

一键下载电路中,三极管 Q1 在 DTR# 为高电平时导通,Q2 在 RTS# 为低电平时导通。根据 CH340G 的数据手册可知,DTR# 和 RTS# 默认输出高电平。在默认状态下,Q1 导通,Q2 阻断,NRST 为高电平,BOOT0 为低电平,主控默认从 Flash 中启动。

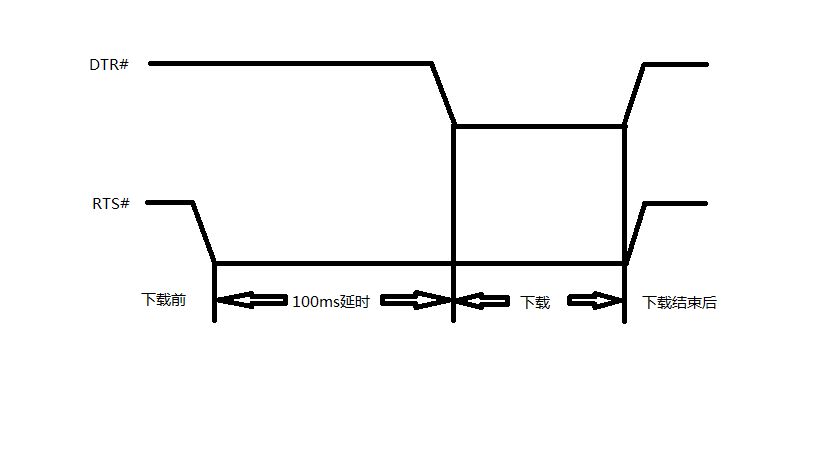

要使得主控进入 ISP 烧录模式,DTR# 和 RTS# 需要产生以下时序。

1、开始时。DTR# 和 RTS# 均为高电平,Q1 导通,Q2 阻断,NRST 为高电平,BOOT0 为低电平。

2、下载前。DTR# 为高电平,RTS# 为低电平,两个三极管均导通,NRST 为低电平,BOOT0 为高电平,为芯片进入 ISP 下载模式做准备。

3、开始下载。DTR# 为低电平,RTS# 为低电平,此时 Q1 阻断,Q2 导通。NRST 为高电平,BOOT0 为高电平。NRST 由低到高时,BOOT0 为高电平,芯片进入 ISP 烧录模式。

4、下载结束。DTR# 和 RTS# 均为高电平,Q1 导通,Q2 阻断,NRST 为高电平,BOOT0 为低电平。

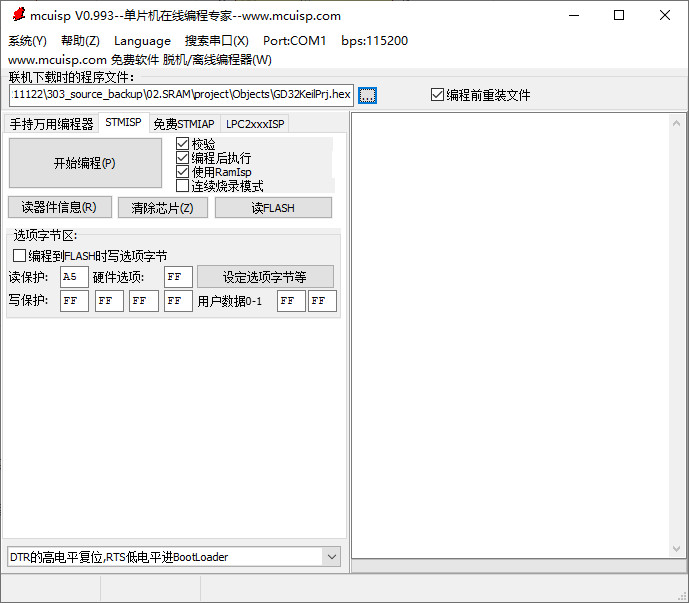

所以,在 MCUISP 下载小工具中,烧录程序时,要选择“DTR的高电平复位,RTS低电平进BootLoader”。如果勾选了“编程后执行”,那么程序下载完成后,MCUISP 小工具还将产生一个复位时序,控制单片机从 Flash 中启动。

JTAG 下载

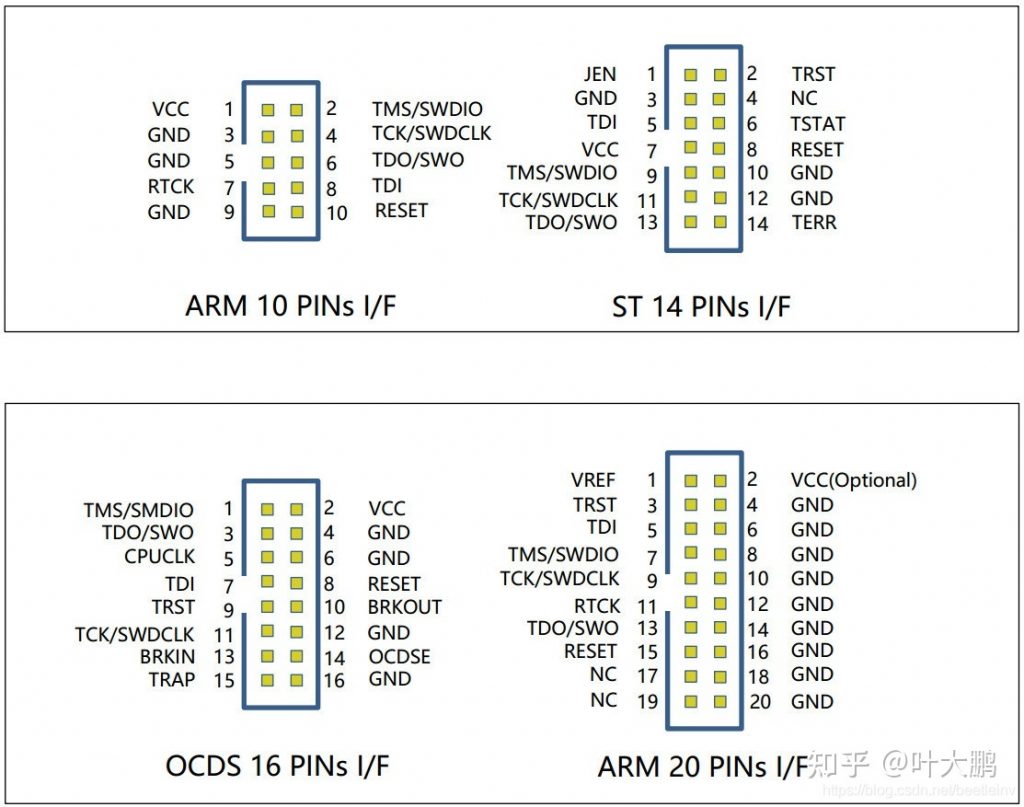

JTAG 接口应用广泛,在 ARM、DSP 和 FPGA 上都有用到。在 Keil 开发环境中,使用 JTAG 接口的电路板,可以字节点击下载按钮更新程序,还能断点调试,十分方便。JTAG 使用 ICP 下载方式。JTAG 接口定义如下,在 STM32 中,因为官方提供的下载器是 20P 的,所以常用的 JTAG 接口也是 20P的。

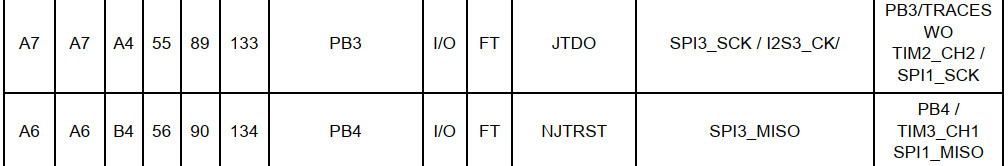

一般来说,JTAG 在单片机上的接口引脚是固定的,通常会在数据手册中给出。对于 STM32F103RCT6 的数据手册,对于 JTAG 引脚都有特别表明,如下所示。

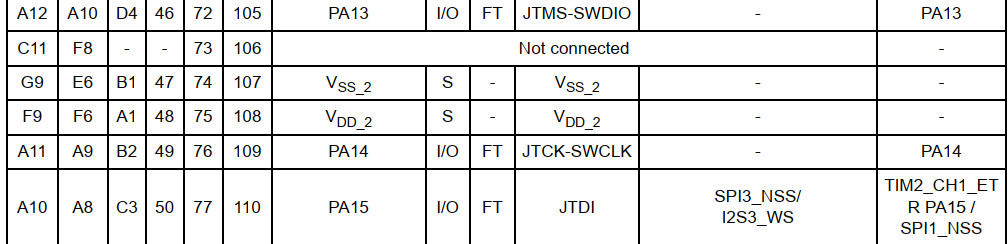

JTAG 接口的使用示例如下所示。

布局完成后,JTAG 接口如下所示。

SWD 下载

从上图可以看出,JTAG 接口还是比较大的,如果电路板对尺寸有要求,那么可以使用 SWD 接口下载程序。

SWD 接口可以由 JTAG 接口转出。相比于 JTAG,SWD 接口通常只需要四根线,极简状态下,只需要三根信号线即可。SWD 和 JTAG 接口一样,同样具备下载、单步调试的功能。JTAG-SWD 转接板如下所示(可以双向转换)。

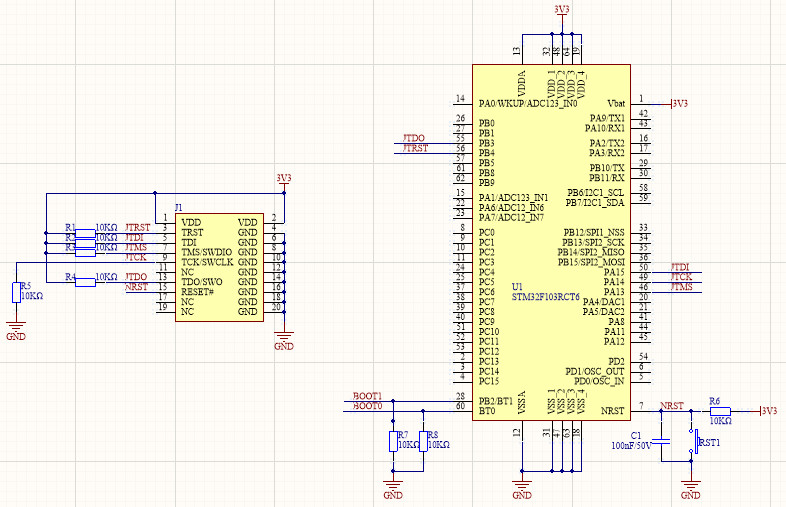

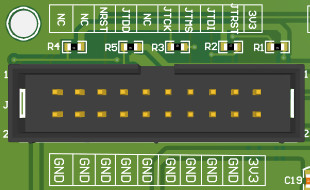

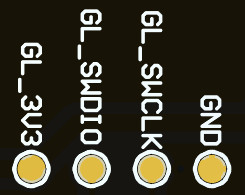

因为 SWD 接口信号很少,甚至不需要在电路板上留出额外的 SWD 下载接口,只需要预留几个焊盘即可,如下所示。

时钟电路设计

STM32F103RCT6 的 OSC_IN(PD0) 和 OSC_OUT(PD1) 可以用来连接外部高速晶振或时钟源,OSC32_IN(PC14) 和 OSC32_OUT(PC15) 可以用来连接 32.768k 低速晶振。

如果项目中有涉及到 RTC 实时时钟,那么建议使用 32.768k 晶振,这会显著提高 RTC 时钟精度。如果对时序要求不高,可以直接使用单片机内部 8MHz 时钟源,那个时钟源虽然不太准,但一般是够用的;如果对时序要求很高、特别高,建议使用外部时钟源。对于 STM32F103RCT6,外部时钟源可以有三种选择、无源晶振、无源晶振和其它时钟源。

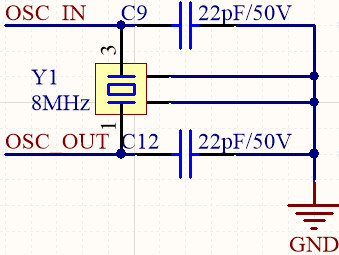

无源晶振

无源晶振的驱动电路如下所示。一般无源晶振是两个引脚,且不分正负。一些比较好的无源晶振会有四个引脚,多出来的两个引脚用于接地,抗干扰性更强。将无源晶振的两个引脚直接接到 OSC_IN 和 OSC_OUT,然后再配置使用外部晶振即可。PCB 布局时,晶振要尽量靠近主控摆放,同时晶振的负载电容也要靠近晶振摆放。

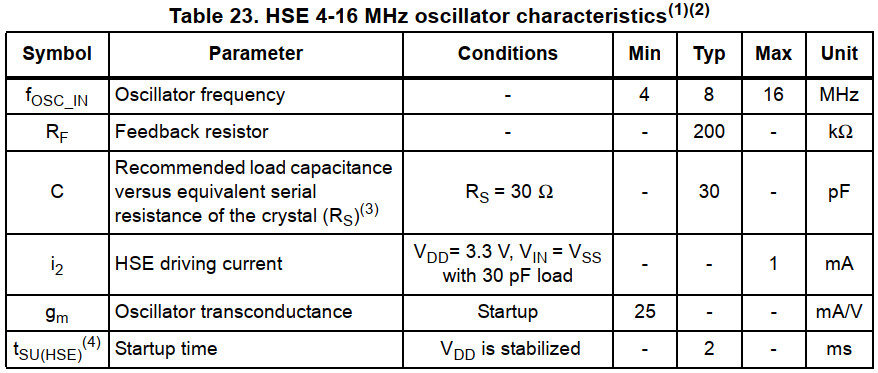

对于 STM32F103RCT6,外部高速无源晶振的频率取值范围为 4~16MHz,如下所示。一般而言,为了获得最高的性能,选择外部高速晶振选型的时候,要结合芯片的 PLL 外设,即时钟倍频外设。所选的晶振频率倍频后,要能达到系统时钟最大值。

有源晶振

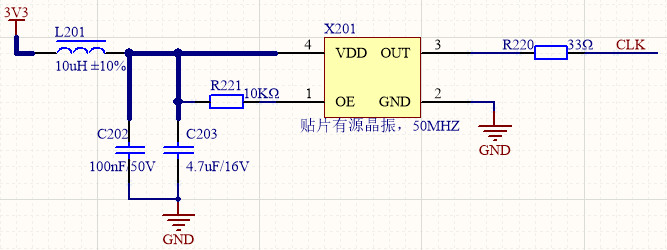

如果电路板对抗干扰性要求很高,那么也可以选用抗干扰能力更强的有源晶振。有源晶振的驱动电路如下所示。驱动有源晶振时,需要为有源晶振提供电源。有源晶振可以直接输出时钟信号,使用时直接将输出的时钟信号连接到主控的 OSC_IN 引脚即可。注意:STM32F103RCT6 使用有源晶振时,需要开启 HSEBYP,即外部高速时钟旁路功能。因为 STM32F103RCT6 芯片内部带有无源晶振驱动模块,搭配无源晶振使用。现在,因为有源晶振直接输出了时钟信号,所以我们需要把这部分电路旁路,即直接跳过无源晶振驱动模块,直接输入到单片机内部。

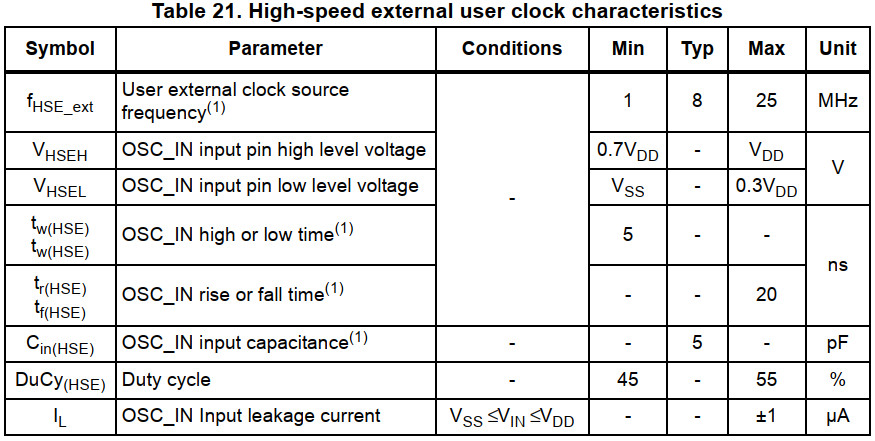

对于 STM32F103RCT6,有源晶振的频率取值范围是 1~25MHz,如下所示。

其它时钟源

既然 STM32F103RCT6 可以用有源晶振做为外部高速时钟源输入,那么我们也可以用其它 MCU 或 FPGA 输出一个时钟信号,驱动 STM32F103RCT6 运行。这样做的目的是为了实现两颗芯片的时钟同步。当两颗芯片需要做高速的数据传输时,注意是高速传输,时钟同步尤为重要。时钟同步可有效降低数据传输过程中的误码率,提高整个系统的稳定性。